# Lecture Notes in Computer Science

3555

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

New York University, NY, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Tullio Vardanega Andy Wellings (Eds.)

# Reliable Software Technology – Ada-Europe 2005

10th Ada-Europe International Conference on Reliable Software Technologies York, UK, June 20-24, 2005 Proceedings

#### Volume Editors

Tullio Vardanega University of Padua Department of Pure and Applied Mathematics via G. Belzoni 7, 35131 Padua, Italy E-mail: tullio.vardanega@math.unipd.it

Andy Wellings University of York Department of Computer Science Heslington, York, YO10 5DD, UK E-mail: andy@cs.york.ac.uk

Library of Congress Control Number: 2005927232

CR Subject Classification (1998): D.2, D.1.2-5, D.3, C.2-4, C.3, K.6

ISSN 0302-9743

ISBN-10 3-540-26286-5 Springer Berlin Heidelberg New York ISBN-13 978-3-540-26286-2 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springeronline.com

© Springer-Verlag Berlin Heidelberg 2005 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 11499909 06/3142 543210

# **Preface**

Started on the inspired initiative of Prof. Alfred Strohmeier back in 1996, and spawned from the annual Ada-Europe conference that had previously run for 16 consecutive years, the International Conference on Reliable Software Technologies celebrated this year its tenth anniversary by going to York, UK, where the first series of technical meetings on Ada were held in the 1970s.

Besides being a beautiful and historical place in itself, York also hosts the Department of Computer Science of the local university, whose Real-Time Group has been tremendously influential in shaping the Ada language and in the progress on real-time computing worldwide. This year's conference was therefore put together under excellent auspices, in a very important year for the Ada community in view of the forthcoming completion of the revision process that is upgrading the language standard to face the challenges of the new millennium.

The conference took place on June 20–24, 2005. It was as usual sponsored by Ada-Europe, the European federation of national Ada societies, in cooperation with ACM SIGAda. The conference was organized by selected staff of the University of York teamed up with collaborators from various places in Europe, in what turned out to be a very effective instance of distributed collaborative processing. The conference also enjoyed the generous support of 11 industrial sponsors.

This year's conference was very successful indeed. It attracted the largest number of submissions in years, from as many as 15 countries worldwide, which made the selection process tougher than ever. Overall, the conference program included 21 carefully selected and refereed papers assigned to 8 thematic sessions spanning a variety of high-profile subjects. The technical program included an industrial track, a first in the conference's history, which encompassed 10 contributions illustrating challenges faced by a cross-section of high-integrity software industry in Europe and the US. As usual, the conference program was itself bracketed by two full days of tutorials, with a special half-day presentation on the new Ada 2005 language, offered by four of its lead designers: John Barnes, Alan Burns, Pascal Leroy and Tucker Taft. Furthermore, three keynote presentations, delivered by John McDermid, Martin Thomas and Bev Littlewood, respectively, marked the opening of each of the main conference days. Finally, much in keeping with the well-established tradition of the conference series, the program made provisions for an excellently populated vendor exhibition and for a halfday vendor session, in which participants were able to catch up with the latest advances in reliable software technology products.

Let us now go into the details of some of the conference highlights.

The invited talks were as follows:

- Prof. John McDermid, University of York, UK

Model-Based Development of Safety-Critical Software

where the opportunities and challenges of model-based development were discussed.

- Prof. Martyn Thomas, Thomas Associates, UK Extreme Hubris

- where the principles of Extreme Programming were critically examined and an alternative manifesto for dependable software development was proposed.

- Prof. Bev Littlewood, City University, London, UK

Assessing the Dependability of Software-Based Systems: a Question of Confidence where the controversial contention was made that dependability claims ought to be associated with a probability-based assessment of the inherent uncertainty about the truth of the claim.

The technical sessions of the program ranged from the illustration of successful applications and distributed systems, to the discussion of design, analysis and implementation methodologies, to formal methods, certification and verification, through to the latest advances with Ravenscar technology, to finish with Ada-related concerns regarding education and language implementation issues.

The tutorial program gathered the following assortment of topics and international expert speakers

- Developing Web-Aware Applications in Ada with AWS, Jean-Pierre Rosen, Adalog, France

- Correctness by Construction A Manifesto for High Integrity Systems, Peter Amey and Neil White, Praxis High Integrity Systems, UK

- Real-Time Java for Ada Programmers, Benjamin M. Brosgol, AdaCore, US

- SAE Architecture Analysis and Design Language, Joyce Tokar, Pyrrhus Software, US and Bruce Lewis, US Army

- High-Integrity Ravenscar Using SPARK, Brian Dobbing, Praxis High Integrity Systems, UK

- Software Safety Cases, John McDermid and Rob Weaver, University of York, UK

- Requirement Engineering for Dependable Systems, William Bail, The MITRE Corporation, US

- Software Fault Tolerance, Patrick Rogers, AdaCore, US

- Programming with the Ada 2005 Standard Container Library, Matthew Heaney, On2 Technologies, US

in addition of course to a special half-day session where four of the lead designers of Ada 2005, John Barnes, Alan Burns, Pascal Leroy and S. Tucker Taft, provided an extensive overview of the new features introduced by the language revision.

A number of people crucially contributed to the success of the conference. First and foremost the authors of all the papers, talks and presentations, for it was from their contribution that the conference was put together. The Program Committee members helped promote the conference in their own circles and also successfully solicited submissions from a variety of authors. The same members along with a number of others also devoted considerable effort to refereeing the submissions in a thorough and timely fashion. The program itself was put together by a smaller group including the Conference Chair, Alan Burns, the Program Co-chairs, Tullio Vardanega and Andy Wellings,

the Tutorials Chair, Iain Bate, the Exhibition and Industrial Track Chair, Rod Chapman, and Dirk Craeynest, representing Ada-Europe. Selected PC members also undertook to shepherd some papers to their final versions. All of these people deserve our gratitude, along with the local organizers, in particular Ian Broster, also in charge of the conference publicity along with Dirk Craeynest, and Sue Helliwell, who oversaw the administrative details of the registration process.

We trust the attendees enjoyed both the technical and social program of the conference, and we close this volume with the confidence of a job well done and the satisfaction of a thoroughly enjoyed experience.

June 2005 Tullio Vardanega

# **Organization**

#### **Conference Chair**

Alan Burns, University of York, UK

# **Program Co-chairs**

Tullio Vardanega, University of Padua, Italy Andy Wellings, University of York, UK

#### **Tutorial Chair**

Iain Bate, University of York, UK

#### **Exhibition and Industrial Track Chair**

Rod Chapman, Praxis High Integrity Systems, UK

# **Publicity Co-chairs**

Ian Broster, University of York, UK Dirk Craeynest, Aubay Belgium, Katholieke Universiteit Leuven, Belgium

# **Local Organization Administrator**

Sue Helliwell, University of York, UK

# **Ada-Europe Conference Liaison**

Laurent Pautet, ENST Paris, France

### **Other Program Committee Members**

Lars Asplund, Mälardalens Högskola, Sweden

Alejandro Alonso, Universidad Politecnica de Madrid, Spain

Janet Barnes, Praxis High Integrity Systems, UK

Guillem Bernat, University of York, UK

Johann Blieberger, Technische Universität Wien, Austria

Bernd Burgstaller, Technische Universität Wien, Austria

Ulf Cederling, Vaxjo University, Sweden

Alfons Crespo, Universidad Politecnica de Valencia, Spain

Raymond Devillers, Université Libre de Bruxelles, Belgium

Michael González Harbour, Universidad de Cantabria, Spain

Andrew Hately, CEATS Research Development Simulation Centre, Hungary

Günter Hommel, Technischen Universität Berlin, Germany

Stefan Kauer, EADS Dornier, Germany

Hubert Keller, Institut für Angewandte Informatik, Germany

Yvon Kermarrec, ENST Bretagne, France

Jörg Kienzle, McGill University, Canada

Fabrice Kordon, Université Pierre & Marie Curie, France

Albert LLamosi, Universitat de les Illes Balears, Spain

Franco Mazzanti, Istituto di Scienza e Tecnologie dell'Informazione, Italy

John McCormick, University of Northern Iowa, USA

Javier Miranda, Universidad Las Palmas de Gran Canaria, Spain

Juan A. de la Puente, Universidad Politecnica de Madrid, Spain

Erhard Plödereder, Universität Stuttgart, Germany

Alexander Romanovsky, University of Newcastle upon Tyne, UK

Jean-Pierre Rosen, Adalog, France

Edmond Schonberg, New York University and AdaCore, USA

Jörgen Winkler, Friedrich-Schiller-Universität, Germany

#### Referees

Alejandro Alonso Las Asplund Khaled Barbaria Janet Barnes Guillem Bernat Johann Blieberger Maarten Boasson

Ian Broster Bernd Burgstaller

Ben Brosgol

Alan Burns Ulf Cederling John Clark Dirk Craeynest Alfons Crespo Raymond Devillers Claude Dutheillet Javier Esparza

Michael González-Harbour

Andrew Hately Günter Hommel

Erik Hu

Jerome Hugues Alexei Iliasov Stefan Kauer

Hubert Keller

Yvon Kermarrec

Jörg Kienzle

Fabrice Kordon

Albert Llamosi

Moreno Marzolla

Franco Mazzanti

Javier Miranda

John McCormick Laurent Pautet Juan A. de la Puente Erhard Plödereder Alexander Romanovsky Jean-Pierre Rosen

Bo Sandèn

Edmond Schonberg Tullio Vardanega Thomas Vergnaud Andy Wellings Jörgen Winkler

# **Table of Contents**

# **Applications**

| ILTIS - The Legacy of a Successful Product  Neville Rowden                                                      | 1   |

|-----------------------------------------------------------------------------------------------------------------|-----|

| A Reference Control Architecture for Service Robots Implemented on a Climbing Vehicle                           |     |

| Francisco Ortiz, Diego Alonso, Bárbara Álvarez,<br>Juan A. Pastor                                               | 13  |

| An Ada Framework for QoS-Aware Applications  Luís Miguel Pinho, Luis Nogueira, Ricardo Barbosa                  | 25  |

| Design and Scheduling Issues                                                                                    |     |

| Efficient Alternatives for Implementing Fixed-Priority Schedulers  Sergio Sáez, Vicent Lorente, Silvia Terrasa, |     |

| Alfons Crespo                                                                                                   | 39  |

| A New Strategy for the HRT-HOOD to Ada Mapping  Matteo Bordin, Tullio Vardanega                                 | 51  |

| Using the AADL to Describe Distributed Applications from Middleware to Software Components                      |     |

| Thomas Vergnaud, Laurent Pautet, Fabrice Kordon                                                                 | 67  |

| Formal Methods                                                                                                  |     |

| Extending Ravenscar with CSP Channels  Diyaa-Addein Atiya, Steve King                                           | 79  |

| Dynamic Tasks Verification with QUASAR                                                                          |     |

| Sami Evangelista, Claude Kaiser, Christophe Pajault,<br>Jean Francois Pradat-Peyre, Pierre Rousseau             | 91  |

| Proving Functional Equivalence for Program Slicing in SPARK <sup>TM</sup>                                       |     |

| Ricky E. Sward, Leemon C. Baird III                                                                             | 105 |

# **Ada and Education**

| Teaching Software Engineering with Ada 95  Daniel Simon, Gunther Vogel, Erhard Plödereder                                       | 115 |

|---------------------------------------------------------------------------------------------------------------------------------|-----|

| A Comparison of the Mutual Exclusion Features in Ada and the Real-Time Specification for Java <sup>TM</sup> Benjamin M. Brosgol | 129 |

| Certification and Verification                                                                                                  |     |

| Smart Certification of Mixed Criticality Systems  Peter Amey, Rod Chapman, Neil White                                           | 144 |

| Non-intrusive System Level Fault-Tolerance  Kristina Lundqvist, Jayakanth Srinivasan, Sébastien Gorelov                         | 156 |

| Distributed Systems                                                                                                             |     |

| Observing the Development of a Reliable Embedded System  Devaraj Ayavoo, Michael J. Pont, Stephen Parker                        | 167 |

| RT-EP: A Fixed-Priority Real Time Communication Protocol over Standard Ethernet                                                 |     |

| José María Martínez, Michael González Harbour                                                                                   | 180 |

| Distributing Criticality Across Ada Partitions  Miguel Masmano, Jorge Real, Alfons Crespo, Ismael Ripoll                        | 196 |

| Language Issues                                                                                                                 |     |

| The Implementation of Ada 2005 Interface Types in the GNAT Compiler Javier Miranda, Edmond Schonberg, Gary Dismukes             | 208 |

| Integrating Application-Defined Scheduling with the New Dispatching Policies for Ada Tasks                                      |     |

| Mario Aldea Rivas, Javier Miranda, Michael González Harbour                                                                     | 220 |

| The Application of Compile-Time Reflection to Software Fault Tolerance Using Ada 95                                             |     |

| Patrick Rogers, Andy J. Wellings                                                                                                | 236 |

# **Ravenscar Technology**

| GNAT Pro for On-board Mission-Critical Space Applications  José F. Ruiz | 248 |

|-------------------------------------------------------------------------|-----|

| The ESA Ravenscar Benchmark  Romain Berrendonner, Jérôme Guitton        | 260 |

| Author Index                                                            | 273 |

# **ILTIS - The Legacy of a Successful Product**

#### Neville Rowden

Siemens Switzerland Ltd., Transportation Systems, Industriestrasse 42, CH-8304 Wallisellen, Switzerland neville.rowden@siemens.com

**Abstract.** ILTIS is probably the most versatile modern railway control and supervisory system available today. From its initial conception in 1990 to the present day, Siemens has been upgrading ILTIS with further functionality while maintaining the quality of original product. The aim of this paper is to analyse what have been the contributing factors in ensuring this success and how this success can be maintained for the future.

#### **Abbreviations**

| CMMI | Capability | Maturity | Model | Integrated |

|------|------------|----------|-------|------------|

|      |            |          |       |            |

CTC Centralised Traffic Control

DEC Digital Equipment Corporation

GUI Graphic User Interface

HP Hewlett Packard

ISO International Organization for Standardization

LAN Local Area Network

MMI Man/Machine Interface

OSF Open System Foundation

SBB Swiss National Railways (Schweizerische Bundesbahnen)

SIL Safety Integrity Level

#### 1 Introduction

ILTIS (an acronym in German for "Integrated Traffic Control and Information System"; it also German for polecat) is a centralised traffic control (CTC) system developed initially for the Swiss National Railways (SBB). All of the software has been written in Ada83 and was originally targeted to DEC's OpenVMS operating system using Alpha computers. On average, 20 developers are employed with ILTIS at any given time adding further functionality to the system.

From humble beginnings, ILTIS has expanded beyond all expectations. Not only is the system currently targeted to OpenVMS (now HP OpenVMS) but also to Microsoft's Windows. The customer base has also expanded dramatically including not only all SBB operating centres, but also those in Austria, Malaysia (national and a private railway), Hungary, Slovenia, Poland, Vietnam and many of the myriad private

T. Vardanega and A. Wellings (Eds.): Ada-Europe 2005, LNCS 3555, pp. 1 – 12, 2005.

railway companies in Switzerland. Several other countries around the world are also expressing interest.

Software projects do not have a good reputation. As a general rule, the larger the project, the greater the chance of failure. ILTIS projects manifest themselves as releases producing additional functionality with respect to the previous release, with projects continuing for an average of 12 months (depending on the complexity of the new features) from the formulation of the system requirements to the final validation.

A recent survey in the United States (see Reference 1., Chapter 1) has found that the cost of an average project ranges from \$430,000 to \$2,300,000. ILTIS releases can, therefore, be considered as larger than average projects. The following statistics were also presented from the same survey:

- only 16% of projects are completed on schedule

- 31% are cancelled, primarily because of quality problems

- 53% cost more than planned, exceeding their budgets by an average of 189%

- projects that reach completion delivered an average of only 42% of the originally planned features.

Experience with ILTIS has shown that it continually bucks the trend (as yet, there have been no major failures) and it would perhaps be interesting to look back and analyse why ILTIS projects have enjoyed so much success.

#### 2 ILTIS Basics

The control and supervision of a railway network requires the acquisition and provision of all data relating to the state of the tracks within the area of responsibility. To accomplish this, CTC (Centralised Traffic Control) computers store and process information, which is received from the local interlocking and the remotely controlled stations. They enable a simple and exact overview of all train movements in the controlled area to be presented to the stationmaster.

A CTC can cover a radius of about 100 km and manages several stations - 30 is a typical number, although there are installations, which control 75 stations.

A CTC system has three basic functions, viz.:

- 1. the central control of the interlockings, e.g.:

- routing trains,

- controlling individual elements (points, signals, etc.),

- blocking/clearing the routes for train traffic,

- blocking/clearing the operation of points,

- emergency commands to override the interlocking in the event of a breakdown.

- 2. the automation of train traffic:

- tracking trains,

- automatic routing,

- transferring train position information to a higher level management centre

- 3. the display of train information for passengers.

Before ILTIS's conception, existing CTC systems and their previous generations were generally developed piecemeal, based on *ad hoc* requirements of a customer's needs. They were loosely coupled together over a LAN (Local Area Network). Every computer in the network was usually dedicated to fulfilling a particular task within the CTC system, e.g. a computer dedicated to tracking trains, another dedicated to the display of train information, etc. The stationmaster was then confronted with a working environment, in which commands to the control system had to be issued via one of the several terminals available to him, each terminal given access to a particular CTC computer. In addition to the ergonomic disadvantages of these CTC systems, there are also inherent disadvantages in the design caused by:

- heterogeneous infrastructure,

- duplication of configuration data (although this in itself is not a problem, there was a danger of inconsistencies appearing in the data unless tight controls were incorporated to prevent it), and

- duplication of resources such as printers, one of which needed to be connected to each computer to register errors.

ILTIS is composed from a network of (upto 40) computers. It was designed from scratch as a totally integrated CTC system, based on the experiences of developing previous CTC systems. Instead of dedicating computers to a particular function, the CTC functions were freely distributable within the available computers. No computer was dedicated to one particular task.

Another radical departure (at least in 1990) was that the stationmaster's work place was to be based on a workstation with a single PC-keyboard and a pointing device (e.g. a mouse). Each workstation can control upto 6 full-graphic colour screens.

All dataflow in the system is over the LAN, making it accessible to every computer connected to the LAN. Information to and from the interlockings is also transmitted directly over the LAN. Similarly, peripheral devices that utilise serial interfaces (such as printers and the system clock) communicate with the LAN through a terminal server. This characteristic enables each computer in the system to take over the functionality of another computer in the event of hardware problems.

#### 3 ILTIS Man/Machine Interface

Probably the most important component of a CTC system is its MMI (Man/Machine Interface). It is of the utmost importance that the MMI can provide clear, concise information concerning the state of the interlockings, and enable the stationmaster to issue error-free commands quickly and efficiently.

#### 3.1 Display Information

The stationmaster has, depending on the system configuration, a number of graphic displays available to him. Using standard window techniques, various windows are accessible to provide clear presentations of the state of the total system and allow any necessary modifications to the system to be made. These windows can be displayed when required and removed from the screen when they are no longer needed, facilitating rapid access to target windows. Earlier CTC systems used screens onto

which information defining the state of the interlockings was displayed as a collection of semigraphic symbols. This severely restricted the amount of information that could be displayed onto a single screen. Even average-sized stations would be forced to be placed onto two screens.

ILTIS is in a position to manipulate full-graphic, colour symbols. Much more information can therefore be concentrated onto a single screen, reducing the need to split stations over several screens. Indeed, using standard window technology, several stations can be displayed simultaneously onto one screen. When necessary, windows can be readily overlaid by the user on top of each other.

The display of the interlocking state information is uniform for each type of interlocking, whether it is a relay-based interlocking or an electronic interlocking. All important messages in the system are displayed by a central message manager in a window containing four sections dedicated to:

- operating requests,

- · operating messages,

- faults, and

- system messages.

It is also possible to configure individual messages so that they are emphasised with different audio tones. Once the message has been noted, it can be acknowledged or cancelled by the stationmaster.

#### 3.2 Commands

Commands are issued via the mouse without any keyboard being involved (commands in earlier CTCs were entered as coded text). Entering commands with a mouse not only increases the speed at which commands can be sent, but also reduces the chances of executing any incorrect commands through typing errors. Interlocking commands are issued by pointing the cursor at the target element with the mouse. With a single mouse click, a popup menu displays the commands, which are currently valid for that element. The available commands are not only determined by the element type (i.e. if it is a barrier, or a main signal, etc.) but also by its current dynamic state. It would, for example, be meaningless offering a command to open a particular barrier, if that barrier were already open.

Once a command has been selected, it is displayed in a text format within the window. The stationmaster has then to acknowledge this command with a single mouse-click before the system allows the command to be executed by the interlocking.

#### 3.3 Language

Another important characteristic of a MMI is the ability to present textual information in the language of the user. This problem is particularly acute in countries like Switzerland, which boasts four national languages. It is, therefore, important that each work place in the CTC system is able to switch online to the language of the current user. Of course, the choice of language should not be restricted to the Latin character set, but should be able to handle the full gamut of character sets (e.g. Cyrillic, Arabic, etc.).

Multilanguage MMI was a basic design consideration in ILTIS and it was a surprisingly much underestimated problem in software development before the concept Unicode existed. In ILTIS, a user can not only define in which language the workstation should present text, but can also decide in which language the various log files (e.g. system log files, fault log files, critical command log files, etc.) should be printed out.

#### 3.4 On-line Maintenance

ILTIS has its own maintenance software integrated into the design. When a maintenance engineer has the necessary privileges, he is able to supervise or modify certain aspects of the running system. This is particularly useful in localising any unexpected problems and for collecting information, which can be analysed at later time by the system developers.

### 4 ILTIS Architecture Requirements

The ILTIS architecture was required to satisfy the following basic requirements:

- Safety

- Availability

- Scalability

- Portability

- Maintainability

- Generic software

#### 4.1 Safety

In certain installations (e.g. in Switzerland and Austria), it is necessary to be able to by-pass the inherent safety of an interlocking to provide an uninterrupted service even in the event of hardware faults and breakdowns.

In these installations, it is essential that a CTC system is able to fulfil certain safety-related functions, i.e.

- it has to ensure that the station-master does not make life-endangering decisions based upon faulty information presented to him by the CTC system,

- it has to ensure that so-called critical commands (i.e. the commands which bypass the safety of an interlocking) cannot be inadvertently executed, and

- critical commands have to be correctly executed.

#### 4.2 Availability

The availability of a CTC system is becoming an increasingly important factor as railway networks become more and more dependent upon them. Current systems usually tackle this problem by having redundant computers, which can be manually switched into service whenever they are needed. From experience, it has been seen that this design suffers from a number of drawbacks, viz.:

- The redundant computers are not in active service. When a situation arises where they need to be brought into service, they themselves could have developed technical problems, which, as the redundant computers are dormant, have gone unnoticed.

- As each computer in the distributed system needs to have a similarly configured redundant computer, this effectively doubles the number of required computers if a full stand-by capability is needed.

In ILTIS the necessary redundancy has been built into the software architecture. No ILTIS task is dedicated to a particular computer but can execute on any available computer in the system. In this way, ILTIS uses a technique of redundant software instead of redundant hardware.

#### 4.3 Portability

ILTIS was designed to be in service for at least 25 years. As it has now passed the halfway point in its life cycle and is not showing any signs of age, ILTIS will be probably reach this goal. In 1990 (as now), it was impossible to predict how the target platforms would change. It was, therefore, important to choose a development language that would facilitate porting to different hardware platforms and operating systems.

#### 4.4 Maintainability

Again, in order to satisfy the expectation of a 25-year product life, ILTIS needed an architecture, which would allow ease of extending functionality without degrading existing functionality.

#### 4.5 Generic Software

ILTIS has not been developed for a single target installation. It is a generic system, which has to be instantiated onto a target installation using configuration data. The software that runs in every Swiss installation is exactly the same as that running, for example, in the Malaysian installations.

Configuring ILTIS installations is not trivial and requires considerable engineering effort. Because of the complexity of configuring target installations, a configuration tool was also developed in parallel to ILTIS.

#### **5** Success Stories

#### 5.1 Ada as Development Language

Ada was predestined for this development. ILTIS is a SIL 2 system and Ada is

highly recommended for developing such systems (see Reference 2., Table A.15).

In 1990, it was clear that Ada should be chosen as the development language but

even today, no other language is available that can compete with Ada when safety

is a factor.

- The cleanly defined constructs in Ada (strong typing, package structure, etc.) not only helps in the area of safety, but also when the target system needs to be robust and of a high quality. ILTIS must be in service 24 hours a day, 7 days a week. The railway traffic in Switzerland never stops and it is essential that a CTC is always in service. Even short breaks in service would have devastating consequences in a country that has the densest railway-traffic in the world. Software quality and reliability are, in effect, prerequisites for any system that has safety requirements.

- In a project of ILTIS's magnitude (3 million lines of code and still counting) and longevity, ease of maintenance is an important factor in the success of the product. Again, Ada's constructs support the developer when he is required to make changes in existing code.

Changes are brought about not only by customers changing requirements but also by the fact that ILTIS is in a continuous state of further development (the latest release contained 46 new features). Development for new markets in other countries often requires changes in sensitive parts of the system as each individual country usually has its own methods for handling railway-traffic. Again, such changes can only be made with confidence if the development language offers the necessary support.

• The target operating system for the first ILTIS installations (OpenVMS on Alpha platforms) is approaching the end of its life. In addition, many customers want to use the cheaper Windows platforms for their installations. Because of these market forces, it was necessary to port ILTIS from OpenVMS to Windows. Portability was built into the original system architecture and, as Ada is operating system independent, it was possible to port the vast majority of the code without any significant problems. Of course, the GUI caused problems and calls to the operating system (which were minimised and isolated in the original architecture) had to be specially handled, but all problems were resolved. ILTIS is now currently supported under OpenVMS and Windows.

The goals of the port actually went further than the ILTIS target platform. A complete development environment for ILTIS is now available under Windows. This has also helped to keep the product alive by reducing the cost of workstations and increasing productivity by using the more advanced development-tools under Windows such as graphical editors.

The port in itself was not totally without problems. Operating system specific code needed to be handled with conditional compilation through a pre-processor, which needed to be custom-developed by Siemens. DECnet connections needed to be replaced with TCP/IP and, although an Ada95 compiler was used for Windows, new code still needed to be restricted to the Ada83 constructs to allow compilation for the target OpenVMS systems.

Interestingly, the Windows Ada95 compiler has a switch, which should have enforced Ada83 compatibility. This, unfortunately, did not cover all cases. A subcontractor for Siemens (the company White Elephant) resolved this problem by customising the editor to perform a syntax check for Ada83 compatibility before submitting it to the compiler. This check could have only been otherwise possible by compiling directly on an OpenVMS system.

• With the risk of appearing to be a Luddite, the fact that Ada is not at the forefront of modern technology is, in fact, a Godsend for developers. Perpetual change is a

nightmare for the maintenance of large systems. Changes in a compiler or operating system result in the need to repeat the full suite of system tests (especially relevant for SIL 2 systems). With Ada's stability, problems or language restrictions are well known and can usually be worked around.

With respect to stability, ILTIS has been doubly blessed. Not only does Ada offer a stable compiler but the main target operating system (OpenVMS) has also offered a stable and robust platform on which ILTIS can be developed and run. It has been a winning combination for the last 15 years, which has only recently been disrupted by the planned phasing out of OpenVMS.

#### 5.2 On-site Customer

• Another factor in the success of ILTIS was having the customer (initially the SBB) involved in all stages of the original development. The concept of the on-site customer is one of the basic tenets of Extreme Programming and it has much to recommend it. Of course, not all projects can afford the luxury of an on-site customer but his advice and perpetual availability for clarification of requirements expedited the development significantly. Unfortunately, this is no longer possible. ILTIS is now being targeted to many customers (not just the SBB) and there is powerful trend within Siemens to satisfy the more formal methods of CMMI.

#### 5.3 Clearly Defined Architecture

• The aim for all system architectures should be to keep it as simple as possible while allowing for the flexibility for further development. The key to the ILTIS architecture was to integrate the concepts of reliability (in the form of redundant components) and of safety (in the form of dual-channelled processing when required) within the basic system architecture. As these concepts were embedded in the system architecture, it necessitated the component developers to take these factors into account within each component design.

#### **5.4 Enforced Component Structure**

All basic component functions in ILTIS (inter-component communication, processing of configuration-data, component start-up, etc.) can only be undertaken by instantiating generic system software. This not only facilitated central points of reference for error localisation and monitoring but also enforced a similar basic design structure for all components. As ILTIS currently contains over 60 components, maintenance and ease of understandability for new developers in the project has been enhanced by the similar design structure of the components.

#### 5.5 Use of Standards

As portability was always an issue in the ILTIS development, standards were used

wherever possible. This was most evident not only with Ada but also with the GUI

where OSF Motif was chosen for all interactions with the user. Again this

facilitated the porting of ILTIS to Windows where the Ada bindings in the ILTIS

code were correspondingly modified.

### 6 Lessons Learnt from Bitter Experience

#### 6.1 Development Resources Should Be Available in the Future

• To contrast with all the advantages of developing within a stable environment, the world has unfortunately not stood still. As Ada is no longer flavour of the month, it has become increasingly more difficult to find experienced developers. In addition, although there are many tools to help in the development of Java, etc., there is almost nothing available for Ada.

Even porting to Windows presented its own set of problems. The number of available Ada compilers for Windows was definitely limited and, at end of the day, there was not much to choose from. The consequences of changing compilers in a project are that all system tests need to be repeated. This was necessary for the port from OpenVMS to Windows. For cost reasons, this is an exercise that can be undertaken only when it is absolutely necessary. Under OpenVMS, ILTIS is still being developed using Ada83. Although the code in Windows compiles with an Ada95 compiler, all new code still needs to be Ada83 compatible so that it can also compile under OpenVMS.

#### 6.2 Manage Changes of Development Processes

- As with most large companies, Siemens has a penchant for changing its development processes. ILTIS is now experiencing:

- its 3<sup>rd</sup> development process, and

- its 3<sup>rd</sup> document management system.

The original ILTIS documents were written in DECwrite. The current documents are written in Word. In ILTIS, the problems of progressing to the next development process, or for using another text-processing tool were never properly addressed. These changes cost time and money, and need to be thought through properly. Such effort is always given a lower priority than new development but eventually everything becomes so cumbersome that further progress is extremely inefficient. ILTIS is addressing this problem at the moment but no satisfactory solutions have been found.

#### 6.3 Invest in a Practical Test Environment

• As ILTIS has been continually extended with further functionality over the previous 15 years, each release has resulted in additional costs for regression testing. These costs have increased exponentially with time and it has been increasingly difficult to maintain the original ILTIS quality whilst keeping the costs to an acceptable level.

The main problem is that the vast majority of the tests are carried out manually. It is, in fact, extremely difficult to automate tests for distributed systems when the real-time aspects and the correctness of the graphical display need to be taken into account. In addition, the generic nature of ILTIS means that endless variations

need also to be tested (it can safely be assumed that no two installations are the same).

Nevertheless, these problems should have been foreseen and addressed during the design phase of the project. Again, no satisfactory solutions have been found. Various attempts with off-the-shelf test automats have not been particularly successful and thought is now being given in developing a custom-built test automat.

#### 6.4 Extract Text Management from Code Development

• It is unbelievable how something as trivial as handling text in different languages could be so difficult. Of course, the aim of the project was always to extricate the text from the code so that installation engineers would be free to define text without impacting the released software. Unfortunately, this was not always possible (most evidently in OSF Motif's UIL files). These file are an integral part of the release and any text corrections in the UIL files, no matter how trivial, result in a new release with the consequent validation process and approval from the governing body.

Also, it is not sufficient to translate text into the target languages. Thought has to be given to window layout which may change due to an increase or decrease in text length. ILTIS currently supports 10 languages and any further text from new functionality needs to be tested for each supported language.

The hope that, by using OSF Motif, all language problems would be consequently solved also proved to be illusionary. ILTIS, Ada83 and OSF Motif all preceded ISO 10646 where most of these issues were finally addressed. Languages covered by ISO Latin 1 were never a problem but it is only in the last release that support has also been provided for ISO Latin 2. Languages such as Cyrillic and Arabic remain a pipe dream.

#### 6.5 Design Tools for Remote Maintenance

• Remote maintenance has become of increasing importance as the number of installations in service increases. This function began as a throwaway feature in the first release and its limitations today are now patently obvious. Although important aspects such as access protection were taken seriously and resolved, not enough time was spent considering how the feature could be designed to be most effective. Remote maintenance was also developed on an *ad hoc* basis without much thought being given to strategy. It is still a useful tool but it would have had an even greater potential if more time had been spent developing a unified design within the system architecture.

#### 6.6 Limit the Scope of Generic Code

• ILTIS code is generic. The same code runs in every installation in Switzerland and the rest of the world. The code needs to be instantiated for each installation using system data (which is also installation-independent) and installation-specific configuration data. The generation of the configuration data is a science unto itself

and can only be undertaken by trained engineers. A data generation and management tool has been developed in conjunction with ILTIS, without which it would be impossible to map an installation's characteristics onto ILTIS-friendly data.

Unfortunately, there was a tendency among developers to relegate unclear specifications to the configuration data, i.e. if it was uncertain what the customer wanted, the choice would have been made configurable. Although this results in much flexibility and versatility, it also causes headaches during the regression test phase where all variations need to be tested. If the variations are not actually used in any installation, this is clearly a waste of resources and also increases the potential for creating errors.

#### 6.7 Standards Can also Be a Millstone

• The reverse side of the standards' coin is that they lose their effectiveness when they are poorly supported. OSF Motif is a case in point. Although OSF Motif may have seemed to be the way forward in 1990, it is anything but today. OSF Motif was an uncomfortable fit with Ada on OpenVMS and it is has been almost perverse using it with Windows today. With OSF Motif on Windows, ILTIS has now become heavily dependent on the whims of another third-party product that, in turn, adds to the complexity of release management.

### 7 Conclusion: From Cutting Edge to Legacy

After many successful years of ILTIS development and deployment, the SBB want to go one step further. Currently, an ILTIS CTC is used to control, on average, 30 stations. The SBB want to connect all ILTIS systems in Switzerland together, creating 12 new control centres (reduced from today's 23 control centres) encompassing 38 cells from which the whole country can be controlled. In the long term, this could even be reduced to just one railway control centre. In order to achieve this, a new project, ILTIS-Netz (or ILTIS-Network in English), was started in 2003 and this is planned to go into service in 2007.

ILTIS-Netz uses ILTIS as its basic component, a cell. The current ILTIS-architecture has been decomposed into its respective layers (3-tier). A new GUI is being developed, which presents the information on the stationmaster's work place by connecting many cells together. The development is being undertaken in Java and it will be interesting to observe how the Ada development interacts with the Java development. The aim of ILTIS-Netz is to replace the View Layer (currently integrated with the Presentation Layer) by a new 5-tier architecture.

As a consequence, ILTIS appears to be heading into the last phase of its life cycle. With respect to ILTIS-Netz, it will be a legacy product. However, there will still be further life in ILTIS as the SBB have many features that they want to be developed in ILTIS in the future. Because of the additional requirements from ILTIS-Netz, future development will be even more demanding than it is today.

### References

- 1. Software Factories Jack Greenfield and Keith Short Wiley Publishing, Inc. 2004

- 2. Deutsche Norm EN 50128 Bahnanwendungen: Telekommunikationstechnik, Signaltechnik und Datenverarbeitungssysteme Software für Eisenbahnsteuerungs- und Überwachungssysteme November 2001

# A Reference Control Architecture for Service Robots Implemented on a Climbing Vehicle\*

Francisco Ortiz, Diego Alonso, Bárbara Álvarez, and Juan A. Pastor

Universidad Politécnica de Cartagena, Spain {francisco.ortiz, diego.alonso}@upct.es

**Abstract.** Teleoperated robots are used to perform hazardous tasks that human operators cannot carry out. The purpose of this paper is to present a new architecture (ACROSET) for the development of these systems that takes into account the current advances in robotic architectures while adopting the component-oriented approach. The architecture is currently being used, tested and improved in the development of an heterogeneous family of robots in the context of the EFTCoR project. It is also presented the Ada'95 implementation of ACROSET for a climbing robot.

#### 1 Introduction

Teleoperated robots are used for extending human capabilities in hazardous and inaccessible environments. Recent progress in mechatronics, perception and computing is opening up a number of new application domains for tele-robotics, but at the same time, the complexity of the applications grows due to the domain characteristics: high variability of functionality and physical characteristics, large variety of execution infrastructures, sensors, actuators, control algorithms, degrees of autonomy, etc.

Despite these differences, teleoperated systems are normally similar from a logical point of view, having many common requirements in their definition and many common components, both logical or physical, in their implementation. As stated in [1], one way of dealing with this complexity is to use architectural frameworks and tools that embody well defined concepts to enable effective realization of systems to meet high level goals. Such an architectural framework allows rapid development of systems and reuse of a large variety of components, with concomitant savings in time and money. There are numerous efforts to provide developers with architectural frameworks of this nature, such as [2, 3, 4].

The objects of this paper are twofold: to present an architectural approach to the development of control units for these kind of systems and to present an example of its use in the development of a real system. The architectural

<sup>\*</sup> This work has been partially supported by European Union (GROWTH G3RD-CT-00794) and the Spanish Government programs CICYT (TIC2003-07804-C05-02) and Seneca (PB/5/FS/02).

$T.\ Vardanega\ and\ A.\ Wellings\ (Eds.):\ Ada-Europe\ 2005,\ LNCS\ 3555,\ pp.\ 13-24,\ 2005.$

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2005

approach, ACROSET, is based on the latest advances in robotic architectures and adopts a component-oriented approach. ACROSET offers a way to re-use the same components in very different systems by separating the functionality from the interaction patterns. It also provides a common framework for developing robot systems and for integrating intelligent behaviours. ACROSET has been implemented and tested in different systems, such as a PLC of Siemens (series 300) and a small FPGA (*Field Programmable Gate Array*), which is a kind of re-programmable hardware. Actually, it is being implemented in Ada'95.

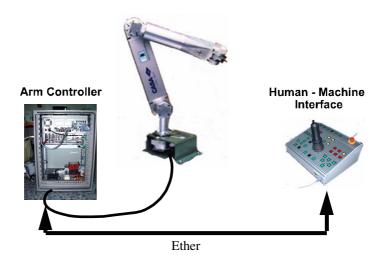

# 2 A Climbing Vehicle in the EFTCoR Project

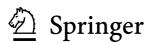

The Environmental Friendly and Cost-Effective Technology for Coating Removal (EFTCoR) project [5,6] is part of the European Industry current effort to introduce environmental friendly ship maintenance. It addresses the development of a solution to the problem of retrieval and confinement of the subproducts obtained from the ship maintenance operation (oxide, paint and adherences mainly). A glance at Fig. 1 shows the difficulty of designing a general purpose system, or even defining a common body of general requirements that could be applied to all systems because: hull dimensions and shapes differ widely, the different areas of any given hull impose very different working conditions for robotic devices, working areas differ in different shipyards or even within the same shipyard and the particular businesses and cultures of shipyards impose different requirements and priorities.

This tremendous variety generates very different problems, which require different robotic systems, each adapted to the specific problem. To solve these problems, a common design pattern has been followed for every robot of the EFTCoR family: they generally consist of a primary positioning system capable of covering large hull areas and a secondary positioning system mounted on

Fig. 1. Different hull shapes in the operational domain

b) Real model

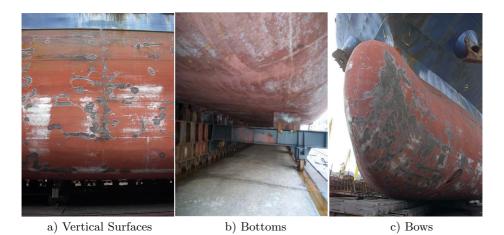

Fig. 2. Different views of the Lázaro vehicle

the primary system that can position a tool over a relatively small area (4 to  $16\ m^2$ ). Different combinations of primary/secondary/tool have been considered and tested. Finally, it is important to stress that the EFTCoR is an industrial project and as such should use components that are common in industrial facilities (PLCs rather than work-stations, field buses rather LANs).

One of the members of the EFTCoR family is the Lázaro vehicle. Lázaro is a caterpillar vehicle capable of scaling a hull thanks to permanent magnets (see Fig. 2), carrying a manipulator that holds a cleaning tool. Like all members of the EFTCoR family, the vehicle can be driven by a human operator and also performs some autonomous tasks, such as obstacle avoidance and simple pre-programmed sequences.

The execution platform is an on-board embedded PC with a PC/104 expansion bus. Its based on an Intel, ultra low voltage Celeron microprocessor. The PC/104 bus is a widely used industrial standard with many advantages, such as vibration-resistance, modularity, mechanical robustness, low power consumption, etc., so its an excellent bus for embedded systems. The expansion system is formed by an analog and digital I/O board featuring 8 analog inputs, 4 analog outputs, 3 timer/counter and 24 general pourpose digital lines, and a PCMCIA expansion interface.

The Lázaro robot has two servomotors to move along the ship hull. The control of each servomotor is performed with the help of both incremental encoders. Besides this, the robot also has a ring of bumpers and infrared sensors to stop in case it gets near an obstacle or collides with it.

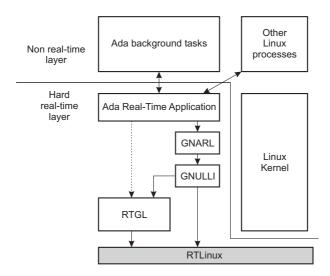

The chosen operating system is Real-Time Linux [7], which makes it possible to have a real-time application running while retaining all the power of a Linux distribution (though with some restrictions) underneath. The Industrial IT Group at the Universidad Politécnica de Valencia has made a GNAT Ada compiler port for the RTLinux operating system [8].

#### 3 The ACROSET Reference Architecture

Considering the differences among systems as noted in sections 1 and 2, a central objective of the proposed architecture must clearly be to deal with such variability. A more precise analysis of the differences among systems [9] reveals that most of them relate not only to the components of the system but to the interactions among these components. Therefore, when designing the architecture the following points (architectural drivers, AD) should be borne in mind:

- **AD1:** Very different instances of the architecture should be able to share the same virtual components.

- **AD2:** The designer should adopt policies that allow a clear separation between the components as such and their patterns of interaction.

- **AD3:** The implementation of such virtual components may be software or hardware; it is highly advisable that such components can be *Commercial off the Shelf* (COTS) components.

- **AD4:** It should be possible to derive concrete architectures for both deliberative (operator-driven) and reactive (autonomous intelligent) systems.

ACROSET (Arquitectura de Control para Robots de Servicio Teleoperados<sup>1</sup>) was designed as a solution to the variability problem found on the EFTCoR project that takes account of the already mentioned architectural drives. It aims to be a reference architecture for teleoperated service robot control units. The architecture emerged from previous works at the DSIE (División de Sistemas e Ingeniería Electrónica, Universidad de Cartagena, Spain) [10, 11] and is currently being used, tested and improved in the EFTCoR project.

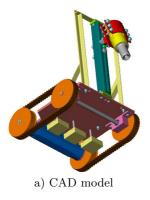

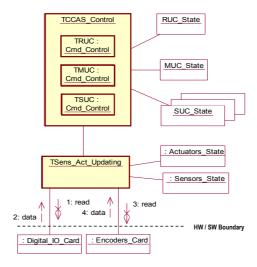

ACROSET (see Fig. 3) is supposed to make it possible for very different systems to use the same components. Therefore, the first step was to define the rules and common infrastructure that would allow components to be assembled or connected. To that end, the concepts of component, port and connector were adopted as defined in [12] and they are the keypoints of ACROSET. A brief description of these concepts is given in section 5.1. The notation followed to describe components, ports and connectors is inspired by the 4 views of Hofmeister [12] and ROOM [13], which extends the UML notation with stereotyped classes and special symbols.

The first subsystem of the architecture is the Coordination, Control and Abstraction Subsystem (CCAS). The CCAS abstracts and encapsulates the functionality of the physical devices of the robot. The CCAS is composed of virtual components, which can be implemented in either software or hardware. The CCAS breaks down into several components, distributed in hierarchical layers (see 3.1). Many of the components used in a robot control unit can be found on the market either as hardware devices and control cards or software packages for a given platform. Where COTS components are used, ACROSET offers the designer two possible solutions: he can define its virtual counterpart or he can use

<sup>&</sup>lt;sup>1</sup> Control Architecture for Teleoperated Service Robots.

Fig. 3. An overview of ACROSET subsystems

the *Bridge* pattern to map an existing virtual component to the actual COTS interface.

To deal with operator-driven and semi-autonomous systems an *Intelligence Subsystem* (IS) is proposed. This way, autonomous intelligence can be added if necessary, to act as another user of the CCAS functionality. This separation of intelligence and functionality enhances the modifiability and adaptability of the system to new missions and behaviours. The intelligence can be combined with the operator commands depending on the application or mode of operation.

A *User Interaction Subsystem* (UIS) is proposed to interpret, combine and arbitrate between orders that may come simultaneously from different users of the system functionality (CCAS), since the system does not concern itself with the source of the order.

Other important aspects besides the functionality or the intelligence of the system include the safety and the possibilities of configuration and management of the application. To differentiate between functionality per se and the monitoring of such functionality, a Safety, Management and Configuration Subsystem (SMCS) is proposed. Another function of this subsystem is to manage and configure the initialisation of the application.

A complete description of ACROSET and one of its instantiations is too extensive to be included in this paper, so only details from one of the subsystems will be presented in the remaining sections. The CCAS has been the selected subsystem because its the most representative and complex subsystem of ACROSET, since it abstracts the robot functionality.

# 3.1 Components of the Coordination, Control and Abstraction Subsystem (CCAS)

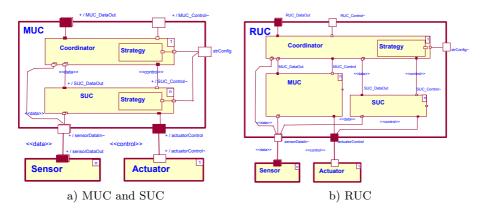

Figure 4 depicts the diagrams of the main components of the CCAS, which are defined and grouped in four layers of granularity:

- **Layer 1:** Composed by the abstraction of the characteristics of atomic components, such as sensors and actuators.

- **Layer 2:** Simple Unit Controller (SUC). SUCs model the control over one actuator of the robot (e.g. a joint).

- **Layer 3:** *Mechanism Unit Controller* (MUC). MUCs model the control over a whole mechanism (e.g. vehicle, manipulator, end effector).

- **Layer 4:** Robot Unit Controller (RUC). RUCs model the control over a whole robot (e.g. a vehicle with an arm and several interchangeable tools).

Every component of the CCAS is composed of two similar objects. On the one hand, it contains a *statechart manager*. This statechart manager decides, depending on the component current state, whether a recently issued command should be executed or not or if the state of the component should change in response to an external signal. It also controls every task created by the component. On the other hand, the object that carries out the component main purpose is interchangeable. This object follows a *Strategy* pattern, so the component behaviour can be modified even at runtime to adapt to a new state and new behaviours can be added later.

Figure 4-a depicts the SUC component. SUCs are meant to control actuators, so the ControlStrategy is the interchangeable object in this case; for example, the ControlStrategy of a given joint may be a traditional control algorithm (PID) or may be changed for a fuzzy logic one. SUCs usually need to accomplish hard real-time requirements and are therefore generally implemented in hardware. When they are implemented in software, they impose severe real-time constraints on operating systems and platforms. In such case, SUCs also need

Fig. 4. CCAS components diagrams

a task to periodically generate the control signal according to the algorithm present in the ControlStrategy object.

Figure 4-a also depicts the *MUC* component. MUC components are logical entities composed of an aggregation of SUCs and a coordinator, which coordinates SUC actions according to the commands and information it receives. The interchangeable object of the MUC is the CoordinationStrategy; for example, the CoordinationStrategy of a given manipulator may be a particular solution for its inverse kinematics. Although the architecture defines MUCs as relational aggregates, they can actually become components (hard or soft) when the architecture is instantiated to develop a concrete system. ACROSET allows the designer decide whether the MUC interface provides access to its inner components or not. In fact, although MUCs may be implemented in either hardware or software, they are very commonly commercial motion control cards that constrain the range of possible commands to its internal components.

Finally, Fig. 4-b shows the *RUC* component. RUCs are an aggregation of MUCs and a global coordinator that generates the commands for its MUCs and coordinates their actions. As in the case of MUCs, the CoordinationStrategy is the interchangeable object. For example, the CoordinationStrategy of a robot composed of a vehicle with a manipulator could be a generalised kinematics solution that contemplates the possibility of moving the vehicle to reach a given target. Like MUCs, RUCs are logical components that can become physical components depending on the concrete instantiation. In general, RUCs are quite complex, comprise both hardware and software elements and can expose a wide variety of interfaces.

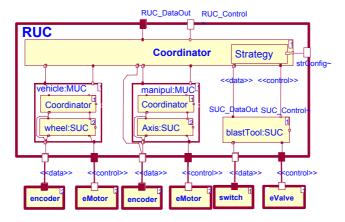

#### 4 Instantiation for the Lázaro Vehicle

Figure 5 shows the CCAS instantiated for this system. As can be seen in the figure, two different MUCs have been implemented: one to control the vehicle and another to control the manipulator. The first contains one SUC to control each of the electrical motors that move the vehicle. The manipulator MUC coordinates two SUCs, one for each manipulator axis. The vehicle uses a tool that consists of an enclosed nozzle for making the blasting and recovering of residues.

The motion controllers have been implemented by means of Ada packages that implement the interfaces defined by ACROSET. In this case, the implementation allows direct access to the hardware without the mediation of any SUC. Two different intelligent behaviours have been added to the IS: obstacle avoidance and simple pre-programmed sequences. The components of the IS that implement these behaviours obtain the information they need from the vehicle sensors and generate commands to the CCAS. Integration between these commands and the operator commands is resolved by an arbitrator in the UIS.

Fig. 5. Components of CCAS in climbing vehicle Control Unit

## 5 Implementation of the Architecture

In the implementation phase, the conceptual view must be mapped to a module view [12]. We have chosen the object-oriented paradigm and Ada95 to implement the architecture, so components, ports and connector will be mapped to classes, objects, associations and dependencies. In this section, some important aspects of the implementation will be presented.

#### 5.1 Ports and Connectors

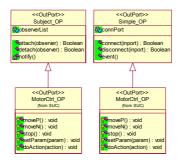

As mentioned in section 3, ACROSET follows a component-oriented approach. Two important concepts when talking about components are the concepts of port and connector. Connectors communicate two compatible ports of two components. Only the functionality offered by the ports of the component can be invoked, using for that the communication protocol encapsulated by the connector. This way, the content of the message is separated from how it is sent.

The concept of *port* is similar to that of interface, but with two differences: ports involved both the operations offered and required by the component and they implement the necessary services to fulfil the communication protocol appropriate to its connector. *Connectors* allow the flow of information between components, and can be as simple as pipes and events or as complex as the client-server protocol.

Changing a connector basically implies the change of the communication protocol between the ports it connects. This variation should be reflected in the modification of the port services referred to the communication, but not of those referred to the component functionality, which is accessed through the port. To separate these concepts (separation of concerns strategy [12]), ACROSET defines as many port types as possible communication ways exist. Port types are defined according to the functionality that they must fulfil (Control Input Port for a SUC, Out Data Port and Input Data for a sensor, etc). Defining the

Fig. 6. Ports and connectors implementation

communication protocol for these last ports is as simple as inheriting from the desired protocol port, as showed in Fig. 6.

#### 5.2 SUC Implementation

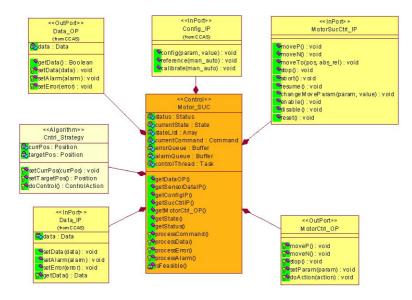

For the same reason that a complete description of ACROSET cannot be described in this paper, only an example of a component implementation is presented in this section. The chosen component is a SUC to control one motor as a representative part of the system (see Fig. 7).

The Motor\_SUC class contains the ports showed in Fig. 6 with stereotypes  $\ll InPort\gg$  and  $\ll OutPort\gg$ , to get data (Data) or produce control (Ctrl) and to configure the SUC (Config). Ports belong to the component and they are created and destroyed with it, so they have a composite relation, as Fig. 7 shows.

Fig. 7. Class diagram of the Motor\_SUC

The operations offered by the control ports match with the events sent by other components to the SUC. Data ports are implemented as generics, showing the same interface to any component. Besides ports, class Motor\_SUC contains the interchangeable ControlStrategy object (the control algorithm).

In case of a Tool\_SUC, all the classes shown in Fig. 7 remain with the same interface, excepting control ports (Ctrl). These ports must be adapted to the control events related to this particular tool.

The rest of components of the instantiation of ACROSET for Lázaro have been built in a similar manner, extending their interfaces to the needs of the system. Notice that the SUC interface remains similar in every component thanks to the method processCommand(), which process any incoming event in its particular control inport, of course, the implementation of that method is different for SUC, MUC and RUC.

#### 5.3 Execution View

Following the 4 views of Hofmeister [12] notation, the execution view describes the structure of a system in terms of its runtime platform elements (tasks, processes, address spaces, etc). In this view, the objects identified in the module view of the system are mapped to a concurrent tasking architecture, where concurrent tasks, task interfaces and interconnections are defined. The driving forces behind the decisions for designing the execution architecture view are performance, distribution requirements and the runtime platform, which includes the underlying hardware and software platforms.

Too many tasks in a system can unnecessarily increase its complexity because of greater inter-task communication and synchronisation, and can lead to increased overhead because of additional context switching. The system designer has to make tradeoffs between introducing tasks to simplify and clarify the design and keeping their number low so that the system is not overloaded.

To help the designer determine the concurrent tasks and to make these tradeoffs, the COMET method [14] provides a set of heuristics which capture expert designer knowledge in the software design of concurrent and real-time system, so called *task structuring criteria*.

Hofmeister proposes as a good starting point to begin by associating each high-level conceptual component with a set of execution elements. Considering that the main objects of the system have been proposed as an instantiation of ACROSET (see Fig. 5), the task structuring criteria might be applied to determine which of the components in the IS, CCAS and SMCS may execute concurrently, and which need to execute sequentially and therefore are grouped into the same task. In a second stage, the task clustering criteria are applied, with the objective of reducing the number of tasks. Figure 8 depicts the task diagram obtained by applying the following task clustering criteria:

**Temporal clustering.** Since the tasks involved in controlling the I/O show no sequential dependency and their activation periods are multiples, they have been grouped in one task.

Fig. 8. Task diagram after clustering

Task inversion. Instead of using a task for each SUC, all identical tasks of the same type have been replaced by one task that performs the same service. Each object state information is captured in a separate protected object. Although SUCs have been grouped, the tasks that perform their concurrent control activities (e.g. a periodic control algorithm) remain as separate tasks, with the task type Cmd\_Control. The same happens with MUC and SUC command control.

**Sequential clustering.** To avoid overloading the system, all the \*UC state control tasks have been grouped in the CCAS task because the information flows up and down always in a sequential order.

#### 6 Conclusions

The use of a common architecture for a domain or family of systems allows rapid developments and the reuse of components. This paper has presented a common architectural framework for the development of teleoperated service robots control units (ACROSET) and also an application example in the context of the EFTCoR project (the Lázaro vehicle), that shows the ability of ACROSET to cope with the needs and requirements of very different systems. The separation of the conventional functionality of the systems (CCAS) from the intelligent behaviours (IS) greatly facilitates the addition of new functionalities and the maintenance of applications.

Perhaps, the main contribution of ACROSET to the current state of the art is the conceptual component oriented approach, which makes the components independent to the implementation language or hardware/software partition. This has allowed implementing those components as PLC blocks, not only as objects and classes, e.g. as CLARAty [2] does.

### References

- E. Coste-Manière and R. Simmons. Architecture: the Backbone of Robotics Systems. In Proc. of the 2000 IEEE International Conference on Robotics & Automation, pages 67–72, April 2000. ISBN: 0780358864.

- I. Nesnas, A. Wright, M. Bajracharya, R. Simmons, T. Estlin, and W.S. Kim. CLARAty: An Architecture for Reusable Robotic System. March 2003. Jet Propulsion Laboratory, NASA.

- 3. K.U. Scholl, J. Albiez, and B. Gassmann. MCA An Expandable Modular Controller Architecture. In 4th Real-Time Linux Workshop, 2001.

- 4. H. Bruyninckx, B. Konincks, and P. Soetens. A Software Framework for Advanced Motion Control. Draft version, January 2002.

- C. Fernández, A. Iborra, B. Alvarez, J.A. Pastor, P. Sánchez, J.M. Fernández-Meroño, and N. Ortega. Co-operative Robots for Hull Blasting in European Shiprepair Industry. *IEEE Robotics & Automation Magazine (Special Issue on Industrial Robotics Applications & Industry-Academia Cooperation in Europe New Tendencies and Perspectives)*, November 2004. ISSN: 1070-9932.

- 6. EFTCoR Official Site. http://www.eftcor.com/.

- M. Barbanov. A Linux-based Real-Time Operating System. PhD thesis, New Mexico Institute of Mining and Technology, June 1997.

- M. Masmano, J. Real, I. Ripoll, and A. Crespo. Running Ada on Real-Time Linux. In *Reliable Software Technologies - Ada-Europe 2003*, volume LNCS 2655, pages 322–333. Springer-Verlag, June 2003.

- 9. J.A. Pastor Franco. Evaluación y desarrollo incremental de una arquitectura software de referencia para sistemas de teleoperación utilizando métodos formales. PhD thesis, Technical University of Cartagena (Spain), 2002.

- F. Ortiz, A. Iborra, F. Marín, B. Álvarez, and J.M. Fernández-Meroño. GOYA: A teleoperated system for blasting applied to ships maintenance. In 3rd International Conference on Climbing and Walking Robots, October 2000. ISBN: 1-86058-268-0.

- A. Iborra, J.A. Pastor, B. Álvarez, C. Fernández, and J.M. Fernández-Meroño. Robots in Radioactive Environments. *IEEE Robotics and Automation Magazine*, 10(4):12–22, December 2003. ISSN: 1070-9932.

- C. Hofmeister, R. Nord, and D. Soni. Applied Software Architecture. Addison-Wesley, January 2000. ISBN: 0-201-32571-3.

- 13. B. Selic, G. Gullekson, and P.T. Ward. Real-Time Object-Oriented Modelling (ROOM). John Wiley and Sons, 1994. ISBN: 0471599174.

- H. Gomaa. Designing Concurrent, Distributed, and Real-Time Applications with UML. Object Technology. Addison-Wesley, 2000. ISBN: 0-201-65793-7.

# An Ada Framework for QoS-Aware Applications

Luís Miguel Pinho, Luis Nogueira, and Ricardo Barbosa

Department of Computer Engineering, ISEP, Polytechnic Institute of Porto, Rua Dr. António Bernardino Almeida, 431, 4200-072 Porto, Portugal {lpinho,luis,rbarbosa}@dei.isep.ipp.pt

**Abstract.** In this paper we present a framework for managing QoS-aware applications in a dynamic, ad-hoc, distributed environment. This framework considers an available set of wireless/mobile and fixed nodes, which may temporally form groups in order to process a set of related services, and where there is the need to support different levels of service and different combinations of quality requirements. This framework is being developed both for testing and validating an approach, based on multidimensional QoS properties, which provides service negotiation and proposal evaluation algorithms, and for assessing the suitability of the Ada language to be used in the context of dynamic, QoS-aware systems.

#### 1 Introduction

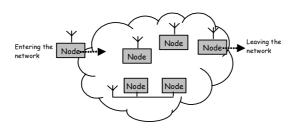

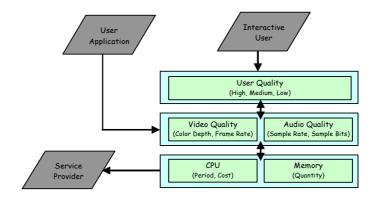

Quality of Service (QoS) is considered an important user demand, receiving wide attention in real-time multimedia research [1][2]. However, in most systems, users do not have any real influence over the QoS they can obtain, since service characteristics are fixed when the systems are initiated. Furthermore, multimedia applications (and their users) can differ enormously in their service requirements as well as in the resources which need to be available to them [3]. These applications present increasingly complex demands on quality of service, reflected in multiple attributes over multiple quality dimensions.

At the same time, the use of laptop computers coupled with wireless network interfaces is growing rapidly. Recent technological development lead to the fusion of wireless ad-hoc networks, peer-to-peer computing and multimedia content. As devices move within the range of each others a local ad-hoc network forms spontaneously, creating a new, highly dynamic and decentralized environment for multimedia applications.

Such an environment is expected to be heterogeneous, consisting of nodes with several resource capabilities. For some of those there may be a constraint on the type and size of applications they can execute with user's acceptable quality of service. For example, video conferencing systems often use compression schemes that are effective, but computationally intensive, trading CPU time for limited network bandwidth. A mobile client with limited CPU and memory capacity, but sufficient link speed, with nearby more powerful (or less congested) devices, can divide the computational intensive processing into tasks and spread it among different neighbours.

T. Vardanega and A. Wellings (Eds.): Ada-Europe 2005, LNCS 3555, pp. 25-38, 2005. © Springer-Verlag Berlin Heidelberg 2005

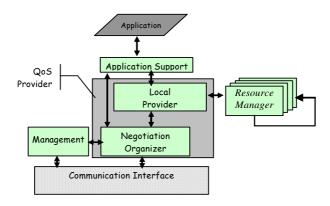

It is obvious that these requirements for more flexible QoS-aware applications impact on the available support from the underlying environment (language, middleware, operating system). In what languages are concerned, Ada has been for a long time considered suitable for the development of traditional, static, real-time applications, but is often considered to be limited concerning the support to more dynamic real-time applications. It is our belief that this latter idea is not true, and, moreover, that Ada is an enabling technology for supporting QoS-aware type of real-time applications

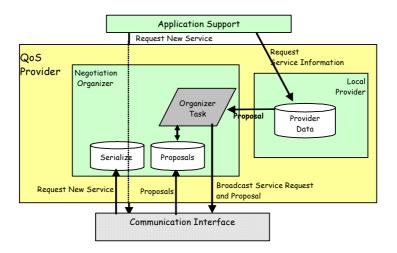

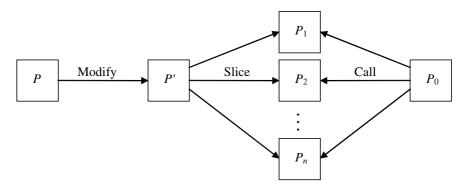

Therefore, in this paper we present a framework which is currently being built for testing and validating a QoS applications support approach which is currently being specified [4]. This framework is being implemented in Ada, using the currently available mechanisms, which will allow providing sufficient insight on the suitability of the language. The rest of this paper is structured as follows. The next section provides a brief description of the considered model for the system, and the used approach for QoS requirements representation and service requests. Section 3 presents an overview of the Ada framework, considering its structure and main functionalities, while sections 4 and 5 present, respectively, how negotiation and acceptance of services is performed, and how resource managers are implemented. Finally, section 6 presents some conclusions.